Ram (Bellek) Nasıl Çalışır? Derinlemesine Teknik Analiz

Giriş: Bilgisayarın Kısa Süreli Hafızası

RAM (Random Access Memory – Rastgele Erişimli Bellek), modern bilgisayar mimarisinin en kritik bileşenlerinden biridir. CPU’nun anlık çalışma alanı olarak görev yapar ve sistem performansını doğrudan belirler. Bu makalede, RAM’in fiziksel yapısından elektriksel işleyişine, okuma/yazma operasyonlarından bellek kontrolcüsüne kadar tüm teknik detayları ele alacağız.

1. RAM’in Temel Mimari Yapısı

Hücre Matris Organizasyonu

RAM, organizasyonel olarak iki boyutlu bir matris şeklinde yapılandırılmıştır:

“`

Sütun 0 Sütun 1 Sütun 2 … Sütun N

Satır 0 [Hücre] [Hücre] [Hücre] … [Hücre]

Satır 1 [Hücre] [Hücre] [Hücre] … [Hücre]

Satır 2 [Hücre] [Hücre] [Hücre] … [Hücre]

… … … … … …

Satır M [Hücre] [Hücre] [Hücre] … [Hücre]

“`

Temel Bileşenler:

Bileşen Fonksiyon Teknik Detay

Memory Cells 1 bit veri saklama Her hücre 0 veya 1 değeri tutar

Address Lines Satır/sütun seçimi log₂(N) adres hattı ile N konuma erişim

Data Lines Veri transferi Genellikle 64-bit (8 byte) veri yolu genişliği

Control Lines İşlem yönetimi RAS, CAS, WE, OE sinyalleri

Adres Çözümleme Mekanizması:

– CPU, istenen bellek adresini adres yoluna yerleştirir

– Satır adresi (Row Address Strobe – RAS) önce aktive edilir

– Sütun adresi (Column Address Strobe – CAS) ikinci aşamada seçilir

– Bu multiplexing tekniği pin sayısını %50 azaltır

—

2. Bit Seviyesinde Veri Saklama: DRAM Hücresi

1T1C (1 Transistor + 1 Capacitor) Yapısı

DRAM’de her bit, bir transistör ve bir kapasitör kullanılarak saklanır:

Mantıksal Durumlar:

– Kapasitör DOLU (yüklenmiş) = Mantıksal 1 (tipik olarak Vcc/2 veya daha yüksek)

– Kapasitör BOŞ (deşarj) = Mantıksal 0 (0V veya toprak potansiyeli)

Neden “Dynamic” RAM?

Kapasitörler doğal olarak kaçak akım (leakage current) sergiler:

Q(t) = Q₀ × e^(-t/RC)

Burada:

– Q₀: Başlangıç yükü

– R: Eşdeğer paralel direnç (kaçak yolu)

– C: Saklama kapasitörü (tipik 25-30 fF)

“`

Yenileme (Refresh) Gereksinimi:

– Yük kaybı nedeniyle veri 64ms içinde bozulur

– Her satır en az 64ms’de bir yenilenmelidir

– Tipik yenileme döngüsü: 8192 satır / 64ms = 7.8μs aralıklarla

– Bu işlem bellek kontrolcüsü tarafından otomatik yönetilir

3. Okuma Operasyonu (Read Cycle)

Adım Adım Veri Erişimi

Detaylı Süreç:

1. Adres Latch (t0): CPU adres yoluna fiziksel adresi yerleştirir

2. RAS Aktivasyonu (t1): Satır adresi içeri alınır, satır dekoder aktive edilir

3. Sense Amplifier Devreye Girer: Seçilen satırdaki tüm hücreler okunur (4-8KB)

4. CAS Aktivasyonu (t2): Sütun adresi seçilir, spesifik bitler belirlenir

5. Veri Çıkışı (t3-t4): Sense amplifier’dan veri çıkış buffer’ına aktarılır

6. Precharge (t5): Bit hatları yeniden şarj edilir (sonraki erişim için hazırlık)

Kritik Zamanlama Parametreleri:

– tRCD (RAS to CAS Delay): Satır-sütun gecikmesi (15ns DDR4)

– tCAS (Column Access Strobe Latency): Sütun erişim gecikmesi (CL14-CL22)

– tRP (Row Precharge Time): Yeni satır erişimi öncesi bekleme

Yıkıcı Okuma (Destructive Read)

DRAM’de okuma işlemi doğası gereği yıkıcıdır:

– Kapasitör, sense amplifier’a bağlandığında yük paylaşımı oluşur

– Orijinal yük seviyesi düşer

– Bu nedenle okuma sonrası otomatik yazma (restore) işlemi gerekir

– Modern DRAM’ler bu işlemi şeffaf şekilde gerçekleştirir

—

4. Yazma Operasyonu (Write Cycle)

Veri Saklama Mekanizması

Yazma Aşamaları:

1. Adres Çözümleme: Hedef hücrenin satır ve sütun adresleri belirlenir

2. Satır Aktivasyonu: Word Line yüksek seviyeye çekilir, erişim transistörü iletime geçer

3. Veri Hazırlığı: CPU veri yolundan gelen bitler write driver’a ulaşır

4. Kapasitör Şarjı/Deşarjı:

– 1 yazılacaksa: Bit Line Vcc seviyesine çekilir, kapasitör dolar

– 0 yazılacaksa: Bit Line 0V’a çekilir, kapasitör boşalır

5. Word Line Kapatma: Transistör kesime girer, yük izole edilir

Yazma Gecikmeleri:

– tWR (Write Recovery Time): Yazma sonrası precharge için bekleme

– tRAS (Row Active Time): Minimum satır aktif kalma süresi

—

5. Bellek Kontrolcüsü (Memory Controller)

Mimari Konum ve Görevleri

Kritik Fonksiyonlar

1. Zamanlama Yönetimi (Timing Control)

– DDR (Double Data Rate) senkronizasyonu

– Komut sıralaması ve arbitraj

– Bank interleaving optimizasyonu

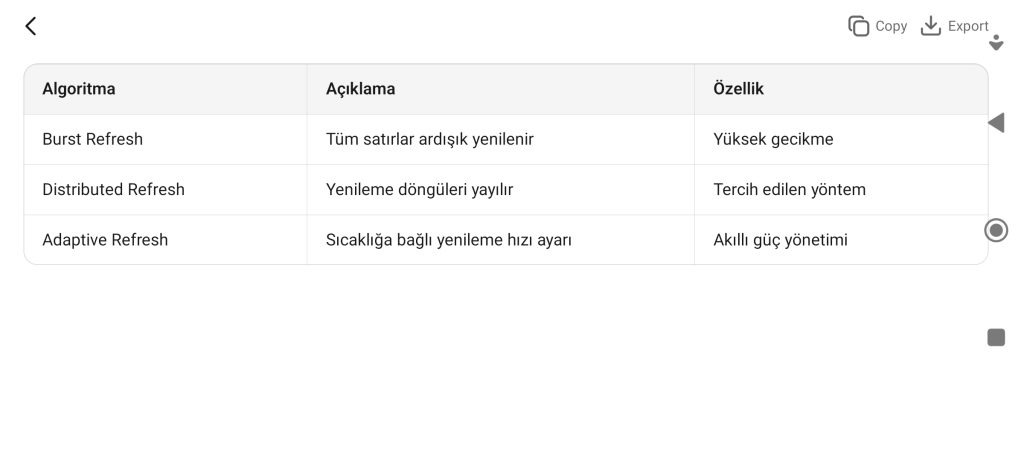

2. Yenileme Yönetimi (Refresh Management)

“`

Refresh Scheduling Algorithms:

├── Burst Refresh: Tüm satırlar ardışık yenilenir (yüksek gecikme)

├── Distributed Refresh: Yenileme döngüleri yayılır (tercih edilen)

└── Adaptive Refresh: Sıcaklığa bağlı yenileme hızı ayarı

“`

3. Güç Yönetimi

– Self-Refresh modu (düşük güç tüketimi)

– Power-Down modları (Active/Precharge Power Down)

– Temperature Compensated Self Refresh (TCSR)

4. Hata Yönetimi

– ECC (Error Correcting Code) hesaplama ve kontrol

– Patrol scrubbing (periyodik arka plan okuma/yazma)

– Spare row/column remapping

6. DRAM vs SRAM: Kapsamlı Karşılaştırma

Devre Seviyesi Farklılıklar

DRAM Hücresi (1T1C):

“`

Basit, yoğun, yavaş, ucuza mal olur

Area: ~6-8 F² (F = minimum feature size)

“`

SRAM Hücresi (6T):

“`

Cross-coupled inverter çifti + 2 erişim transistörü

“`

Karşılaştırma Tablosu

Özellik DRAM SRAM Teknik Gerekçe

Hücre Yapısı 1T + 1C 6 transistör SRAM’te feedback loop stabilite sağlar

Hız 10-20ns latency 0.5-2ns latency SRAM’te kapasitör şarj bekleme yok

Yoğunluk 16 Gb/chip 256 Mb/chip DRAM hücresi 20x daha küçük

Güç Tüketimi Yüksek (refresh) Düşük (static) DRAM’de periyodik yenileme gerekir

Maliyet/Bit 0.00001 0.001 Üretim karmaşıklığı ve alan farkı

Refresh Gerekli (64ms) Gerekmez SRAM cross-coupled yapı sayesinde stabil

Enerji/Bellek Erişimi 10nJ 0.5nJ DRAM’te row activation enerjisi yüksek

Kullanım Senaryoları

DRAM Kullanım Alanları:

– Ana sistem belleği (DDR4/DDR5 DIMM’ler)

– Grafik belleği (GDDR6/X)

– Mobil bellek (LPDDR5)

– Neden: Yüksek kapasite, düşük maliyet, kabul edilebilir hız

SRAM Kullanım Alanları:

– CPU L1/L2/L3 önbellekleri

– TLB (Translation Lookaside Buffer)

– Register dosyaları

– Mikrocontroller embedded memory

– Neden: Ultra-düşük gecikme, deterministik erişim, güç verimliliği

—

7. Modern DRAM Evrimi: DDR5 ve Ötesi

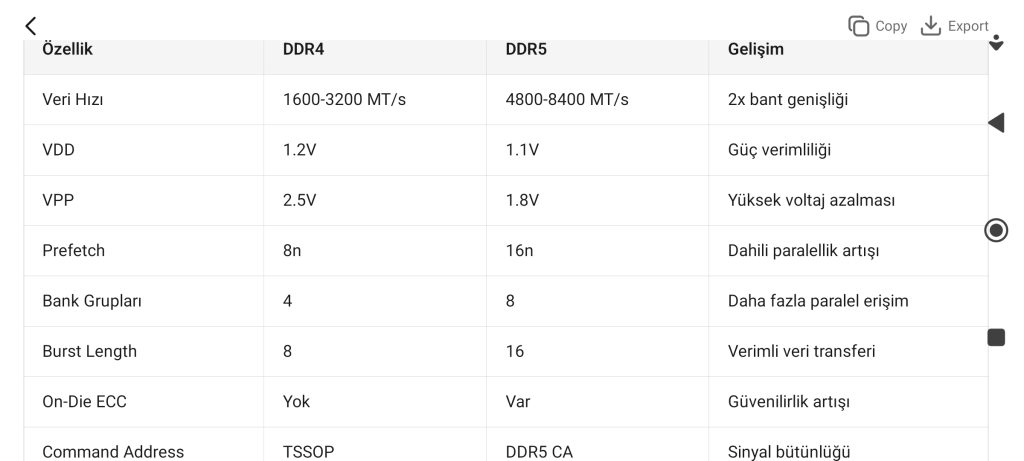

Nesil Karşılaştırması

Özellik DDR4 DDR5 Gelişim

Veri Hızı 1600-3200 MT/s 4800-8400 MT/s 2x bant genişliği

VDD 1.2V 1.1V Güç verimliliği

VPP 2.5V 1.8V Yüksek voltaj azalması

Prefetch 8n 16n Dahili paralellik artışı

Bank Grupları 4 8 Daha fazla paralel erişim

Burst Length 8 16 Verimli veri transferi

On-Die ECC Yok Var Güvenilirlik artışı

Command Address TSSOP DDR5 CA Sinyal bütünlüğü

Gelecek Trendler

HBM (High Bandwidth Memory):

– 3D stack yapı (TSV – Through Silicon Vias)

– 1024-bit geniş veri yolu

– GPU ve AI hızlandırıcılarında kullanım

CXL (Compute Express Link):

– Bellek havuzlama ve genişletme

– Cache coherent interconnect

– Veri merkezi ölçeklenebilirliği

—

Sonuç

RAM teknolojisi, basit bir kapasitör-transistör çiftinden başlayarak karmaşık bir bellek hiyerarşisine evrilmiştir. DRAM’in yoğunluk ve maliyet avantajları ile SRAM’in hız avantajları arasındaki denge, modern bilgisayar mimarisinin temelini oluşturur.

Anahtar teknik noktalar:

– DRAM refresh mekanizması, dinamik yapının bedelidir

– Bellek kontrolcüsü, fiziksel katman ile mantıksal katman arasındaki kritik arayüzdür

– Zamanlama parametreleri (tCAS, tRCD, tRP), gerçek performansı belirler

– Hiyerarşik önbellek yapısı, SRAM ve DRAM’in güçlü yönlerini birleştirir

Gelecekte, bellek-duyarlı hesaplama (processing-in-memory) ve yeni bellek teknolojileri (MRAM, ReRAM, PCM) bu ekosisteme dahil olacak, ancak temel prensipler – hücre yapısı, adres çözümleme ve zamanlama yönetimi – değişmeyecek temel yapı taşları olarak kalacaktır.